CPU 기능

1. 명령어 인출 : 기억장치로부터 명령어를 읽어옴

2. 명령어 해독 : 수행 할 동작을 결정하기 위해 명령어 해독함

-> 모든 명령어들에 대하여 공통적으로 수행

3. 데이터 인출

4. 데이터 처리

5. 데이터 저장

-> 명령어에 따라 필요한 경우에만 수행

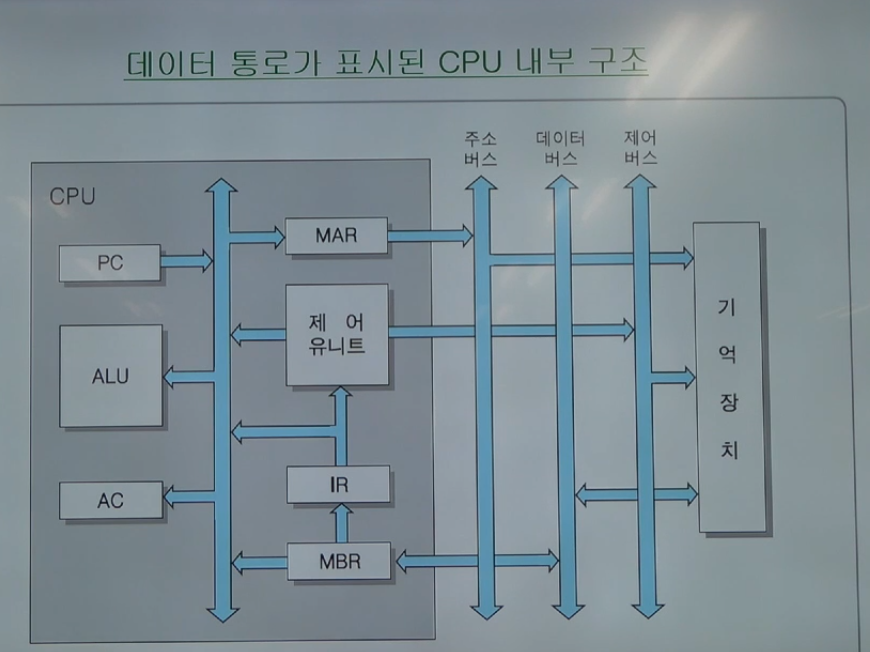

CPU 기본 구조

1. 산술논리연산장치 : 산술 연산, 논리 연산 수행하는 회로로 이루어진 하드웨어 모듈

2. 레지스터 세트 : 엑세스 속도가 가장 빠른 기억장치, CPU 내부 포함할 수 있는 레지스터들의 수가 제한됨

3. 제어 유니트(제어 장치) : 명령어 해석 후 실행을 위한 제어 신호를 순차적 발생

4. CPU 내부 버스 : ALU와 레지스터들 간의 데이터 이동을 위한 데이터 선과 제어 유니트로부터 발생되는 제어 신호 선들로 구성된 내부 버스, 외부 시스템 버스와 직접 연결 X, 반드시 버퍼 레지스터들 혹은 시스템 버스 인터페이스 회로를 통하여 시스템 버스와 접속

명령어 실행

- 명령어 사이클

- 두 개의 부사이클들로 분리

1. 인출 사이클 : 명령어 읽어오는 단계

2. 실행 사이클 : 명령어 실행

명령어 실행에 필요한 CPU 내부 레지스터들

1. 프로그램 카운터 : PC

- 다음 인출할 명령어의 주소를 가짐

- 명령어 인출 후 자동적으로 일정 크기 만큼 증가( 한 명령어 길이)

- 분기(branch) 명령어가 실행되는 경우 목적지 주소로 갱신

2. 누산기 : AC

- 데이터를 일시적으로 저장

- 레지스터 길이는 CPU가 한 번에 처리할 수 있는 데이터 비트 수와 동일

3. 명령어 레지스터 : IR

- 가장 최근에 인출된 명령어 코드가 저자되어 있는 레지스터

4. 기억장치 주소 레지스터 : MAR

- PC에 저장된 명령어 주소가 시스템 주소 버스로 출력되기 전에 일시적으로 저장되는 주소 레지스터

5. 기억장치 버퍼 레지스터 : MBR

- 기억장치에 쓰여질 데이터 혹은 기억장치로부터 읽혀진 데이터를 일시적으로 저장하는 버퍼 레지스터

인출 사이클(마이크로 연산) : 기억장치의 지정된 위치에서 명령어를 읽어오는 방법

첫번째 주기 : 현재 PC 내용을 CPU 내부 버스를 총해 MAR로 전송

t0 : MAR <- PC

두번째 주기 : 주소가 지정되는 기억장치 위치로 읽혀진 명령어가 데이터버스를 통해 MBR로 적재, PC내용에 1을 더함

t1 : BMR <- M|MAR|, PC <- PC + 1

세번째 주기 : MBR에 있는 명령어 코드가 명령어 레지스터 IR로 이동

t2 : IR <- MBR

주기는 주파수의 역수다.

주파수(클록)가 1GHz면 (클록)주기는 1ns(10^-9)다.

실행 사이클 : 명령어 해독, 연산들 수행

연산의 종류

1. 데이터 이동

2. 데이터 처리

3. 데이터 저장

4. 프로그램 제어

기본적인 명령어 형식 및 구성

1. 연산 코드(operation code) : CPU가 수행할 연산 지정

2. 오퍼랜드(operand) : 명령어 실행에 필요한 데이터가 저장된 주소

ex) LOAD addr 명령어 : 기억장치에 저장된 데이터를 CPU 내부 레지스터인 AC로 이동하는 명령어

t0 : MAR <- IR(addr)

명령어 레지스터 IR에 있는 명령어 주소 부분 MAR로 전송

t1 : MBR <- M|MAR|

그 주소가 지정한 기억장소로부터 데이터를 인출하여 MBR로 전송

t2 : AC <- MBR

그 데이터를 AC에 적재

ex) STA addr 명령어 : AC 레지스터의 내용을 기억장치에 저장하는 명령어

t0 : MAR <- IR(addr)

데이터를 저장한 기억장치 주소를 MAR로 전송

t1 : MBR <- AC

저장할 데이터를 버퍼 레지스터인 MBR로 이동

t2 : M|MAR| <- MBR

MBR의 내용을 MAR이 지정하는 기억장소에 저장

ex) ADD addr 명령어 : 기억장치에 저장된 데이터를 AC의 내용과 더하고 다시 AC에 저장

t0 : MAR <- IR(addr)

데이터 저장할 기억장치 주소 MAR로 전송

t1 : MBR <- M|MAR|

저장할 데이터를 버퍼 레지스터인 MBR로 이동

t2 : AC <- AC + MBR

그 데이터와 AC 내용을 더하고 결고값을 다시 AC에 저장

ex) JUMP addr 명령어 : 오퍼랜드가 가리키는 위치의 명령어로 실행 순서를 변경하는 분기(branch) 명령어

t0 : PC <-IR(addr)

명령어의 오퍼랜드를 PC에 저장

다음 명령어 인출 사이클에서 그 주소의 명령어가 인출되므로, 분기가 발생

인터럽트 사이클 : 프로그램 실행 중 CPU의 현재 처리 순서를 중단시키고 다른 동작을 수행하도록 요구

인터럽트 서비스 루틴 : 인터럽트를 처리하기 위하여 수행되는 프로그램 루틴

인터럽트가 들어오면 CPU는 어떤 장치가 인터럽트를 요구했는지 확인 -> 해당 ISR호출

이 후, 중단되었던 원래 프로그램 수행

세부 동작

1. 현재 명령어 실행 끝낸 즉시, 다음 실행 명령어 주소를 스택에 저장 -> 일반적으로 스택은 주기억장치에 특정 부분

2. ISR 호출하기 위해 루틴의 시작 주소 PC에 적재, 이 때 시작 주소는 인터럽트를 요구한 장치로부터 전송되거나 미리 정해진 값으로 결정

인터럽트 마이크로 연산 SP <- SP-1 (SP는 스택 포인터)

t0 : MBR <- PC

PC의 내용 MBR로 전송

t1 : MAR <- SP, PC <- ISR의 시작 주소

PC 내용 인터럽트 서비스 루틴의 시작 주소로 변경

t2 : M|MAR| <- MBR

MBR에 저장되어있던 원래 PC 내용 스택에 저장

다중 인터럽트 처리방법 2가지

1. CPU가 인터럽트 서비스 루틴하는 도중 새로운 인터럽트와도 새로운 인터럽트 사이클 수행X

-> 인터럽트 플래그 : 0 (인터럽트 불가능 상태)

-> 시스템 운영상 중요 프로그램이나 도중 중단할 수 없는 데이터 입출력 동작 등을 위한 인터럽트 처리에 사용

2. 인터럽트 우선순위 정하고, 우선순위 낮은 인터럽트 처리하는 동안 우선순위가 더 높은 인터럽트가 들어온다면 높은 우선순위 인터럽트부터 처리

간접 사이클

명령어 포함되어 이는 주소를 이용하여, 명령어 실행에 필요한 데이터의 주소를 인출하는 사이클

-> 간접 주소지정 방식에서 사용

인출 사이클과 실행 사이클 사이에 위치

간접 사이클 마이크로 연산

t0 : MAR <- IR(addr)

t1 : MBR <- M|MAR|

t2 : IR(addr) <- MBR

'학교수업' 카테고리의 다른 글

| 컴퓨터 그래픽스 기초 3주차 (0) | 2022.03.23 |

|---|---|

| 인공지능개론 3주차 (0) | 2022.03.21 |

| 윈도우즈 프로그래밍 3주차 (0) | 2022.03.17 |

| UNIX서버 2주차 (1) | 2022.03.16 |

| 컴퓨터 그래픽스 기초 2주차 (0) | 2022.03.16 |